Project S05 - Real-Time Material Map

Principal Investigators: Prof. Dr. Diana Göhringer, TUD / Prof. Dr. Thomas Kaiser, UDE

Achieved Results in the 1st Phase

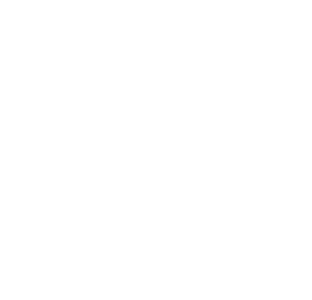

S05 first phase was focusing on enabling material localization and characterization on mobile devices under strong real-time and energy constraints. Therefore, an embedded computing architecture with high-energy efficiency has been realized as shown in Fig. 1.

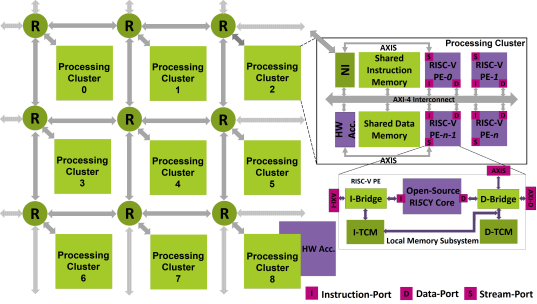

The proposed computing platform is based on a novel scalable many-core computing architecture with hierarchical communication infrastructure. The proposed many-core architecture is based on a modular cluster-based design where each cluster can host multiple homogeneous and heterogeneous processing elements (PEs) based on the target application requirements. Multiple clusters are connected through a scalable and adaptive 2D-Network-on-Chip (NoC) mesh architecture. The architecture is implemented and evaluated on an FPGA platform as shown in Fig. 2. A peak computing performance of 0.8 Giga Operations per second (GOp/s) using 8 clusters with 4 PEs each with an energy efficiency of 0.4 nJ/bit can be achieved on the FPGA.

Fig. 1. Overview of the RISC-V based many-core architecture with a 3x3 mesh NoC with optional HW accelerators."

Fig. 2. Placement of 9 reconfigurable processing clusters and a static 3x3 mesh NoC on the Xilinx Virtex Ultrascale+ XCVU9P floorplan.">

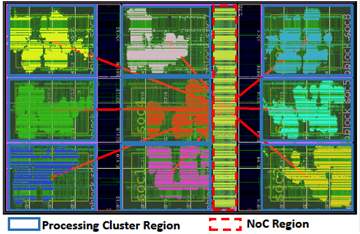

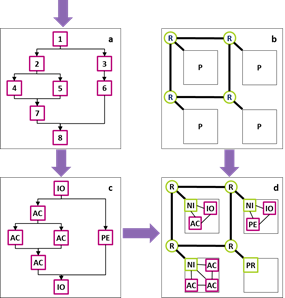

A novel design and programming methodology was investigated including a library as shown in Fig. 3. This methodology creates a mesh-like and partition-based Network-on-Chip (NoC) architecture, based on an application. A major research focus was the compile-time mapping of dataflow applications on partitions of mesh-like architectures.

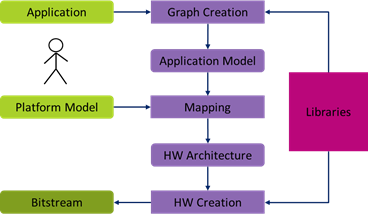

The complete mapping process involves the partitioning of applications into task graphs, mapping these tasks to physical nodes, creating a schedule, clustering these nodes and place them on the partitions of the mesh-like architecture as shown in Fig. 4. The clustering and placement processes were investigated in a novel approach combining several heuristic and load balancing methods and algorithms. The evaluation of the resulting approach shows an algorithm that is scalable with the given problem and rapidly finds a near-optimal solution.

Fig. 3. The complete overview for the novel design and programming methodology "

Fig. 4. The proposed mapping tool flow from a data flow graph to architecture generation."

Project-related publications

For all project-related publications please click here and scroll to the S05 section.